《半導體》高速傳輸、先進封裝、晶片互連…創意多點卡位AI基建升級潮

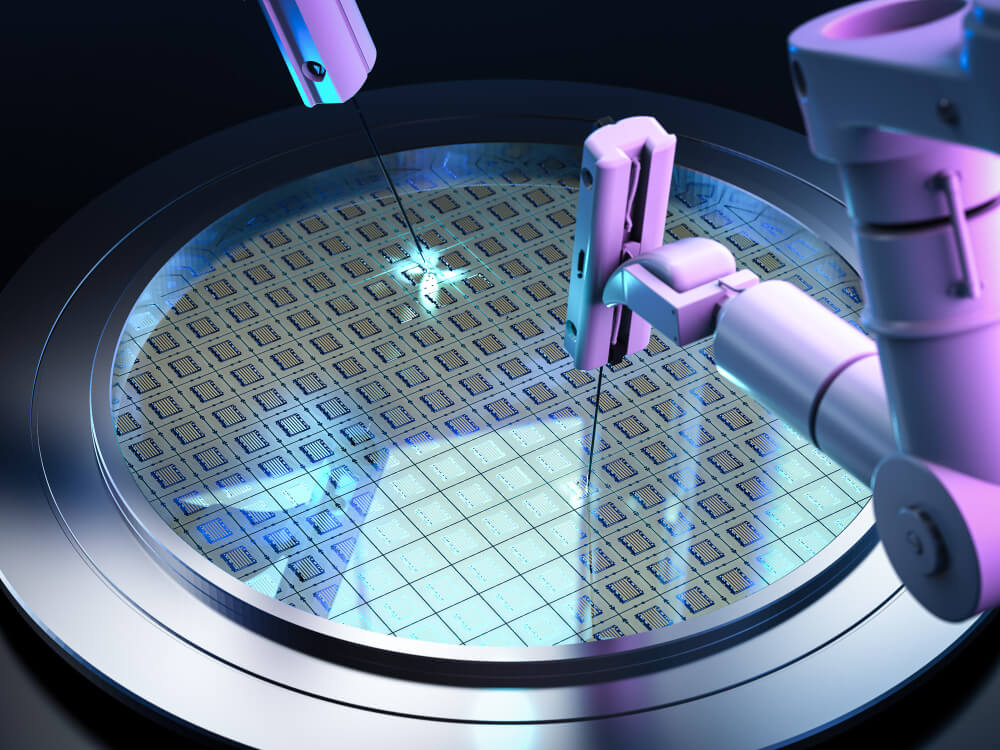

(圖片來源:freepik)

發布時間:2026-04-28 08:40:55

分享

作者:時報新聞

【時報-台北電】台積電子公司創意技術布局全面升級,在AI與高效能運算(HPC)需求持續爆發下,公司持續推進共同封裝光學(CPO)、2奈米HBM及多晶片封裝(MCP)等關鍵技術,從高速傳輸、先進封裝到晶片互連,為下一波AI基礎建設升級潮搶先卡位。 據悉,創意今年預計完成矽光子引擎的3D封裝技術及2奈米HBM4E IP之設計定案,並完成IVR(整合穩壓器)技術設計流程開發,展現其先進製程與高階晶片技術領先地位。 創意預計於5月21日召開股東會,今年將全面改選九名董事,現任董事長曾繁城不參與本次改選並將退休,象徵領導團隊將進行接班,其中,董事候選名單中,台積電研究發展設計暨技術平台(DTP)副總經理魯立忠為新面孔;據悉,DTP為「晶片設計」與「製程技術」之間的橋樑。 隨著晶片設計、晶圓製造難度快速提高,ASIC扮演之角色將愈發重要。創意於技術布局全面加速,在CPO領域,創意藉著整合3奈米電子積體電路(EIC)與65奈米光子積體電路(PIC),並結合矽光子引擎進行3D封裝,已完成設計流程建置,預計後續將進入客戶導入階段。 HBM布局方面,創意已完成3奈米HBM4 12G IP(矽智財)設計定案,並搭配CoWoS先進封裝技術,預計完成矽驗證後導入客戶量產。更受矚目的是,創意正同步開發2奈米HBM4E 16G IP,預計於今年上半年完成設計定案,提前卡位下一世代高頻寬記憶體市場。 在先進電源管理解決方案(IVR)上,創意預計採用16奈米製程,異質整合PMIC、晶圓級電感(OWL)及深溝槽電容(DTC),朝向高效率、低功耗方向演進,呼應AI晶片功耗快速攀升的趨勢。半導體業界分析,AI晶片開始往平台發展,ASIC將與晶圓代工大廠緊密合作,協助晶片大廠節省開發時程及投片管理,設計服務的機會及需求同步擴大,傳統ASIC設計服務,將逐步轉型為AI時代高階系統整合解決方案供應商。(新聞來源 : 工商時報一張珈睿/台北報導)

☞警語:以上媒體報導,非任何形式之投資建議,投資前請獨立思考、審慎評估。nStock網站所有內容僅供APP使用教學參考,並無任何推介買賣之意,投資人應自行承擔交易風險。

網友都在問

熱門排行

上市

上櫃

合併

漲幅

跌幅

成交值

讀取中....