《半導體》搶攻多晶粒世代 神盾小金雞乾瞻推64Gbps高速互連解決方案

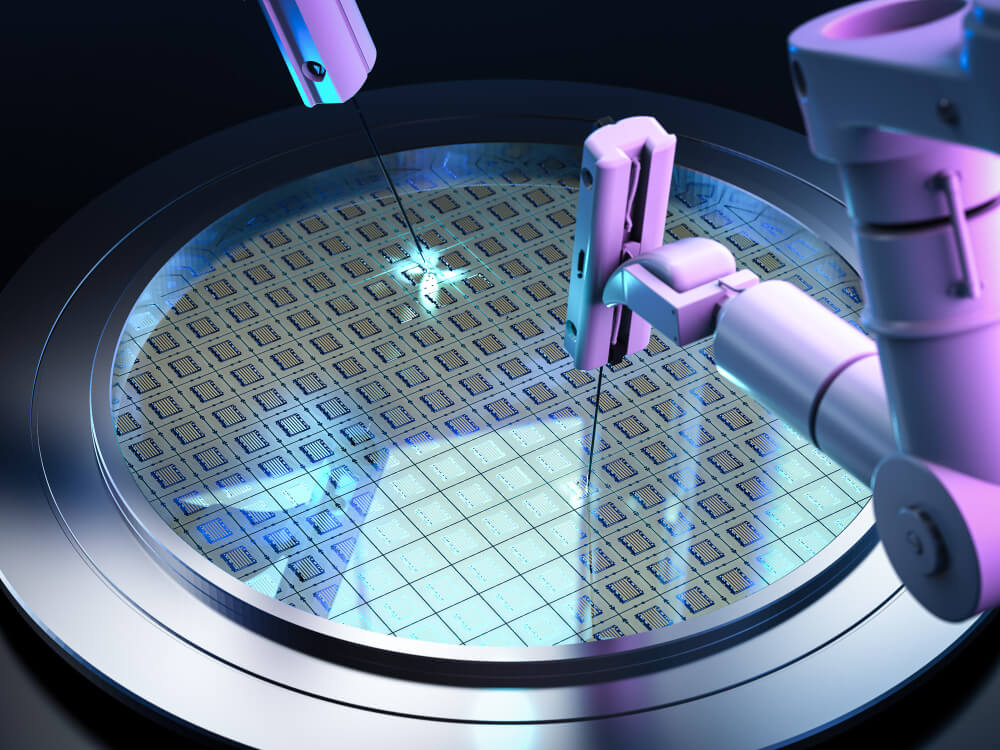

(圖片來源:freepik)

發布時間:2025-08-28 10:33:40

分享

作者:時報新聞

【時報記者王逸芯台北報導】神盾(6462)旗下專注於先進互連與記憶體介面技術的矽智財廠商乾瞻科技,本週正式發佈符合UCIe 3.0標準的64Gbps晶粒間互連PHY+控制器IP設計套件。此方案針對先進3奈米製程進行最佳化,可協助晶片設計團隊加速可行性研究、平面規劃與系統整合,進一步縮短新一代多晶粒系統的產品開發時程。 此次推出的設計套件具備多項關鍵特色。其一,完整符合最新UCIe 3.0規範,並向下相容既有標準,確保設計團隊能在現有架構上無縫延伸。其二,套件結合PHY與控制器,提供多晶粒互連所需的整合式解決方案。在協定支援方面,控制器涵蓋AXI4、CXS.B、CXL、Streaming與PCIe等多種介面,滿足多元應用需求。效能方面,該方案具備更寬的眼圖(data eye)開口,在不依賴FEC(前向錯誤修正機制)的情況下即可達成1E-27位元錯誤率(BER),並支援per-bit即時健康監控功能。其功耗表現亦居業界領先,僅0.2pJ/bit,在兼顧高頻寬與高效能的同時有效降低能耗,並可靈活支援先進封裝與有機基板兩種應用場景。 在應用層面,該套件廣泛適用於高效能運算(HPC)晶粒、xPU與AI晶粒、記憶體擴充晶粒,以及需要高繞線頻寬密度的多晶粒設計,同時亦支援光學I/O晶粒,為新一代系統整合提供強大助力。 乾瞻科技同時為Samsung SAFE IP Program與Intel Foundry Accelerator IP Alliance成員,長期專注於開發高效能、低延遲與低功耗的高速互連及記憶體介面IP,產品已廣泛應用於人工智慧(AI)、高效能運算(HPC)、車用電子及高速光電通訊等領域。憑藉深厚的研發實力與持續創新,乾瞻致力於為全球客戶提供最先進的互連解決方案。 此外,乾瞻科技計畫於本月提交公開發行申請並掛牌興櫃,目標於2026年第二季完成掛牌上櫃,正式進入資本市場。

☞警語:以上媒體報導,非任何形式之投資建議,投資前請獨立思考、審慎評估。nStock網站所有內容僅供APP使用教學參考,並無任何推介買賣之意,投資人應自行承擔交易風險。

今日大量成交股

熱門排行

上市

上櫃

合併

漲幅

跌幅

成交值

讀取中....